HLS——四、接口

本文共 2216 字,大约阅读时间需要 7 分钟。

主要介绍以下intel FPGA HLS接口:

一、avalon-st接口 二、默认HLS接口 三、内存主机接口 四、显示流媒体接口 五、寄存器接口 六、内存从接口例程

D:\intelFPGA\18.1\hls\examples\tutorials\interfaces

一、avalon-st接口

1、用途 1.在Intel®FPGA中用于简化系统设计的简单连接模块 2.用于交互的标准接口设计 HLS编译器围绕HLS模块生成Avalon接口 2、种类 1.Avalon流接口(Avalon-ST) -数据单向流动,界面简单灵活 2.Avalon内存映射接口(Avalon-mm) -典型的基于地址的读/写接口的主从连接 3.其他接口 -管道,三态管道、中断、时钟、复位1.Avalon流接口(Avalon-ST)

数据传输的标准、灵活和模块化协议 -单向 -点对点连接 -完全同步 -支持简单和复杂的接口需求 2.Avalon®-MM接口 基于地址(内存映射)的协议,允许模块使用读/写请求进行通信 主接口 -用于针对特定地址的读/写传输 从接口 -接受和响应转移请求 互联处理对主地址请求的解码,用于实际的从接口、反压、时钟差异等 与时钟接口相关联

2.Avalon®-MM接口 基于地址(内存映射)的协议,允许模块使用读/写请求进行通信 主接口 -用于针对特定地址的读/写传输 从接口 -接受和响应转移请求 互联处理对主地址请求的解码,用于实际的从接口、反压、时钟差异等 与时钟接口相关联  Avalon®接口规范 https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf

Avalon®接口规范 https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf 二、默认接口

1、ip接口 每个模块都包含以下接口 — start,busy,done,和stall 信号 —如果函数不返回void则返回数据, —所有标量参数都会产生输入管道 —所有指针或引用参数都变成地址输入 —所有指针共享一个Avalon内存映射接口,用于从系统内存加载 存储数据自定义接口的一些方法 多种自定义接口的方法 —RTL接口的精准控制 —对C测试平台框架的最小影响 2、模块调用接口 表示对模块的调用和从模块返回的流接口 如果非void,则包含返回数据 模块包含start和busy信号 -start表示启动调用,并设置数据参数 - busy允许模块的反压 模块返回done和stall信号 -done表示返回 -stall允许模块反压

2、模块调用接口 表示对模块的调用和从模块返回的流接口 如果非void,则包含返回数据 模块包含start和busy信号 -start表示启动调用,并设置数据参数 - busy允许模块的反压 模块返回done和stall信号 -done表示返回 -stall允许模块反压

4、指针:隐式内存映射接口 所有指针或引用参数都成为与start和busy信号相关联的地址输入 自动创建内存映射主机接口 默认64位地址空间

4、指针:隐式内存映射接口 所有指针或引用参数都成为与start和busy信号相关联的地址输入 自动创建内存映射主机接口 默认64位地址空间  指针 波形

指针 波形  三、显式MM Master接口 1、使用mm_master<>类显式声明Avalon-MM主机接口 -更好地控制接口 -通过参数指定属性 用法: ihc::mm_master<datatype, /template arguments/>

三、显式MM Master接口 1、使用mm_master<>类显式声明Avalon-MM主机接口 -更好地控制接口 -通过参数指定属性 用法: ihc::mm_master<datatype, /template arguments/>

其他属性包括read_write模式和在HLS编译器参考手册中描述的waitrequest 3、示例:

其他属性包括read_write模式和在HLS编译器参考手册中描述的waitrequest 3、示例:  MM Master—波形

MM Master—波形  4、MM Master的寻址空间 拥有多个地址空间将创建多个MM Master -允许在PD上同时进行多个控制

4、MM Master的寻址空间 拥有多个地址空间将创建多个MM Master -允许在PD上同时进行多个控制  示例:

示例:  四、流接口 标量函数参数成为hdl模块上的流水线输入端口 —Avalon流接口与start、busy输入信号相关联 —隐式 显式流接口 -使用ihc::stream_in<>和ihc::stream_out<>模板类 -通过引用传递 -使用有效和现成的信号创建Avalon流接口 -对接口的显式控制

四、流接口 标量函数参数成为hdl模块上的流水线输入端口 —Avalon流接口与start、busy输入信号相关联 —隐式 显式流接口 -使用ihc::stream_in<>和ihc::stream_out<>模板类 -通过引用传递 -使用有效和现成的信号创建Avalon流接口 -对接口的显式控制 显式流式接口示例

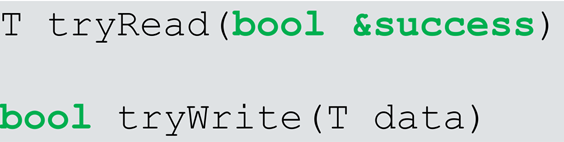

阻塞与非阻塞读写

如果接口无法保持,则阻塞调用read()和write()将暂停模块 -缓冲区为空时读取数据(或如果未缓存且有效,则取消中断) -当缓冲区满时写入(或如果未缓冲和准备就绪时取消中断) 在模块中非阻塞可调用tryRead()和tryWrite() -返回布尔值,以确定调用是否成功 完整的流输入示例

完整的流输入示例

显式流接口波形

显式流接口波形  自定义显式流接口

自定义显式流接口 用法: ihc::stream_in<datatype, /template arguments/>

其他属性包括HLS编译器参考手册中描述的bitsPerSymbol和readylatency

其他属性包括HLS编译器参考手册中描述的bitsPerSymbol和readylatency 流数据包示例

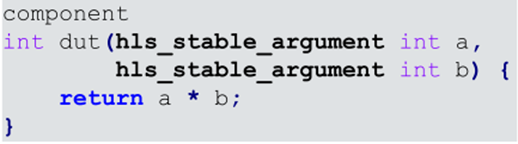

使用包信号允许多个流调用站点 稳定参数 使用连线实现 减少输入数据的流水线级数,可以明显地节省寄存器 在模块调用期间不要更改的变量

稳定参数 使用连线实现 减少输入数据的流水线级数,可以明显地节省寄存器 在模块调用期间不要更改的变量  示例:

示例:  从接口 模块控制和状态寄存器 -代替start/busy/done/stall 信号 从数据寄存器 -适合较小的输入 从存储器 -用于较大的数组 MM Slave模块 模块可以有1个CSR从接口,用于函数调用和返回 - 与从参数共享 -生成的<component_name> _csr.h中描述的地址映射 irq_done表示模块已完成 - 不需要停止 用于代替默认的流调用和返回

从接口 模块控制和状态寄存器 -代替start/busy/done/stall 信号 从数据寄存器 -适合较小的输入 从存储器 -用于较大的数组 MM Slave模块 模块可以有1个CSR从接口,用于函数调用和返回 - 与从参数共享 -生成的<component_name> _csr.h中描述的地址映射 irq_done表示模块已完成 - 不需要停止 用于代替默认的流调用和返回  MM Slave寄存器参数 可以独立于从模块使用 用于代替默认管道参数 适合较小的输入

MM Slave寄存器参数 可以独立于从模块使用 用于代替默认管道参数 适合较小的输入  从模块和寄存器地址映射

从模块和寄存器地址映射  从存储器参数 在模块内部的内存块中实现参数 -通过从接口访问 适用于指针参数 适用于较大的数组 可设置指定字节大小

从存储器参数 在模块内部的内存块中实现参数 -通过从接口访问 适用于指针参数 适用于较大的数组 可设置指定字节大小

系统中的流式HLS模块

系统中的流式HLS模块

系统中HLS模块的内存映射

具有流接口的MM HLS模块

转载地址:http://lugk.baihongyu.com/

你可能感兴趣的文章